مختلف قسم کے منطقی خاندان دستیاب ہیں جو ڈیجیٹل لاجک سرکٹس کو ڈیزائن کرنے میں استعمال ہوتے ہیں۔ ریزسٹر ٹرانزسٹر لاجک (RTL)، Emitter Coupled Logic (ECL)، Diode Transistor Logic (DTL)، Complementary Metal Oxide Semiconductor Logic (CMOS)، اور ٹرانزسٹر-ٹرانسسٹر لاجک (TTL) . ان لاجک فیملیز میں سے، ڈی ٹی ایل لاجک فیملی کا استعمال عام طور پر 1960 اور 1970 کی دہائی سے پہلے زیادہ جدید لاجک فیملیز کو تبدیل کرنے کے لیے کیا جاتا تھا۔ CMOS اور ٹی ٹی ایل۔ ڈایڈڈ ٹرانجسٹر منطق کی ایک کلاس ہے۔ ڈیجیٹل سرکٹس جو ڈائیوڈس اور ٹرانجسٹرز کے ساتھ ڈیزائن کیا گیا ہے۔ لہٰذا ڈائیوڈس اور ٹرانزسٹرز کا امتزاج کافی چھوٹے اجزاء کے ساتھ پیچیدہ منطقی افعال بنانے کی اجازت دیتا ہے۔ یہ مضمون مختصر معلومات فراہم کرتا ہے۔ ڈی ٹی ایل یا ڈایڈڈ ٹرانجسٹر منطق اور اس کی ایپلی کیشنز۔

ڈایڈڈ ٹرانزسٹر لاجک کیا ہے؟

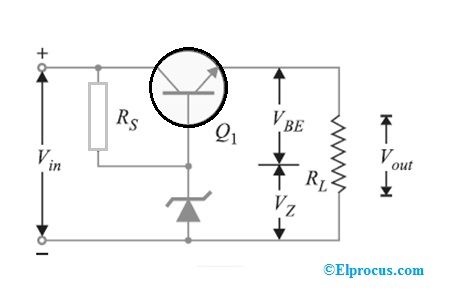

ڈائیوڈ ٹرانزسٹر لاجک ایک لاجک سرکٹ ہے جس کا تعلق ڈیجیٹل لاجک فیملی سے ہے جو ڈیجیٹل سرکٹس بنانے کے لیے استعمال ہوتا ہے۔ اس سرکٹ کے ساتھ ڈیزائن کیا جا سکتا ہے ڈایڈس اور ٹرانزسٹر جہاں ان پٹ سائیڈ پر ڈائیوڈز استعمال ہوتے ہیں اور آؤٹ پٹ سائیڈ پر ٹرانزسٹر استعمال ہوتے ہیں، اس طرح اسے DTL کہا جاتا ہے۔ ڈی ٹی ایل سرکٹ کی ایک مخصوص کلاس ہے جو موجودہ ڈیجیٹل الیکٹرانکس میں برقی سگنلز کی پروسیسنگ کے لیے استعمال ہوتی ہے۔

اس لاجک سرکٹ میں، ڈائیوڈز منطقی افعال انجام دینے میں کارآمد ہوتے ہیں، جب کہ ٹرانجسٹرز کو ایمپلیفیکیشن کے افعال انجام دینے کے لیے استعمال کیا جاتا ہے۔ کے مقابلے میں ڈی ٹی ایل کے بہت سے فوائد ہیں۔ مزاحم ٹرانجسٹر منطق کی طرح؛ زیادہ فین آؤٹ ویلیوز اور زیادہ شور مارجن اس طرح، DTL کو RTL فیملی نے بدل دیا ہے۔ دی ڈایڈڈ ٹرانجسٹر لاجک کی خصوصیات بنیادی طور پر شامل ہیں؛ ڈیجیٹل کلچر لیس، ڈیجیٹل اسٹریٹجسٹ، ڈیجیٹل آرکیٹیکٹ، تنظیمی چست، کسٹمر سینٹرسٹ، ڈیٹا ایڈووکیٹ، ڈیجیٹل ورک پلیس لینڈ اسکیپر اور بزنس پروسیس آپٹیمائزر۔

ڈائیوڈ ٹرانزسٹر لاجک سرکٹ

ڈائیوڈ ٹرانزسٹر لاجک سرکٹ ذیل میں دکھایا گیا ہے۔ یہ دو ان پٹ ڈائیوڈ ٹرانزسٹر لاجک NAND گیٹ سرکٹ ہے۔ اس سرکٹ کو دو ڈائیوڈس اور ایک ٹرانزسٹر کے ساتھ ڈیزائن کیا گیا ہے جہاں دو ڈائیوڈس کو D1 اور D2 کے ساتھ اشارہ کیا گیا ہے اور ریزسٹر کو R1 سے اشارہ کیا گیا ہے جو لاجک سرکٹ کا ان پٹ سائیڈ بناتا ہے۔ Q1 ٹرانزسٹر CE کنفیگریشن اور R2 ریزسٹر آؤٹ پٹ سائیڈ بناتا ہے۔ اس سرکٹ میں 'C1' کپیسیٹر کو سوئچنگ کے پورے وقت میں اوور ڈرائیو کرنٹ دینے کے لیے استعمال کیا جاتا ہے اور اس سے سوئچنگ کا وقت کچھ سطح تک کم ہو جاتا ہے۔

ڈایڈڈ ٹرانجسٹر لاجک ورکنگ

جب بھی A & B سرکٹس کے دونوں ان پٹ کم ہوں گے، تو D1 اور D2 دونوں ڈائیوڈس فارورڈ بائسڈ ہو جائیں گے، اس طرح یہ ڈائیوڈز آگے کی سمت میں چلیں گے۔ اس طرح وولٹیج کی سپلائی (+VCC = 5V) کی وجہ سے موجودہ سپلائی پورے R1 ریزسٹر اور دو ڈائیوڈس میں GND کو فراہم کرے گی۔ R1 ریزسٹر کے اندر وولٹیج کی سپلائی کم ہو جاتی ہے اور یہ Q1 ٹرانزسٹر کو آن کرنے کے لیے کافی نہیں ہو گا، اس طرح Q1 ٹرانزسٹر کٹ آف موڈ میں ہو گا۔ لہذا، 'Y' ٹرمینل پر o/p منطق 1 یا ہائی ویلیو ہوگا۔

جب ان پٹ میں سے کوئی ایک کم ہو، تو متعلقہ ڈایڈڈ فارورڈ بایزڈ ہو گا، اسی طرح کا آپریشن ہو گا۔ چونکہ ان میں سے کوئی بھی ڈائیوڈ فارورڈ بائیزڈ ہے، تو پورے فارورڈ بائیسڈ ڈائیوڈ میں کرنٹ زمین پر فراہم کیا جائے گا، اس طرح 'Q1' ٹرانزسٹر کٹ آف موڈ میں ہوگا، اس لیے 'Y' ٹرمینل پر آؤٹ پٹ ہوگا۔ اعلی یا منطق 1.

جب بھی A اور B دونوں ان پٹ زیادہ ہوں گے تو دونوں ڈائیوڈ ریورس بائزڈ ہوں گے، اس طرح دونوں ڈایڈس کام نہیں کریں گے۔ تو اس حالت میں، +VCC سپلائی سے حاصل ہونے والا وولٹیج Q1 ٹرانزسٹر کو کنڈکشن موڈ میں لے جانے کے لیے کافی ہوگا۔

اس لیے ٹرانجسٹر ایمیٹر اور کلیکٹر ٹرمینلز میں کام کرتا ہے۔ 'R2' ریزسٹر کے اندر پورا وولٹیج کم ہو جاتا ہے اور 'Y' ٹرمینل پر آؤٹ پٹ LOW o/p ہو گا اور اسے کم یا منطق 0 سمجھا جاتا ہے۔

سچائی کی میز

DTL سچائی کی میز ذیل میں دکھائی گئی ہے۔

|

اے |

بی | اور |

|

0 |

0 | 1 |

|

0 |

1 |

1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

ڈایڈڈ ٹرانجسٹر منطق کے پھیلاؤ میں تاخیر کافی بڑی ہے۔ جب بھی تمام ان پٹ لاجک ہائی ہوں گے تب ٹرانجسٹر بیس ریجن میں سیچوریشن اور چارج بلڈ اپس میں چلا جائے گا۔ جب بھی ایک ان پٹ کم ہو تو اس چارج کو ہٹا دینا چاہیے، پھیلاؤ کا وقت بدلنا۔ ڈائیوڈ ٹرانزسٹر لاجک کو ایک طرح سے تیز کرنے کے لیے ریزسٹر R3 میں ایک کپیسیٹر شامل کرنا ہے۔ یہاں، یہ کپیسیٹر بیس ٹرمینل پر جمع چارج کو ختم کرکے ٹرانزسٹر کو بند کرنے میں مدد کرتا ہے۔ اس سرکٹ میں کپیسیٹر پہلی بیس ڈرائیو کو بڑھانے کے ذریعے ٹرانزسٹر کو آن کرنے میں بھی مدد کرتا ہے۔

ترمیم شدہ ڈایڈڈ ٹرانجسٹر منطق

ترمیم شدہ DTL NAND گیٹ ذیل میں دکھایا گیا ہے۔ ریزسٹرس اور کیپسیٹرز کے اجزاء کی بڑی قدروں کو آئی سی پر معاشی طور پر بنانا بہت مشکل ہے۔ لہذا درج ذیل DTL NAND گیٹ سرکٹ کو IC کے نفاذ کے لیے صرف C1 capacitor کو ختم کر کے، ریزسٹر کی قدروں کو کم کر کے اور استعمال کر کے تبدیل کیا جا سکتا ہے۔ ٹرانجسٹر اور ڈایڈس جہاں بھی ممکن ہو۔ یہ ترمیم شدہ سرکٹ صرف ایک ہی مثبت سپلائی کا استعمال کرتا ہے اور اس سرکٹ میں D1، اور D2 diodes کے ساتھ ایک ان پٹ سٹیج، ایک R3 ریزسٹر، اور ایک AND گیٹ شامل ہوتا ہے جس کے بعد ٹرانجسٹرائزڈ انورٹر ہوتا ہے۔

کام کرنا

اس سرکٹ کا کام یہ ہے، اس سرکٹ میں دو ان پٹ ٹرمینلز A اور B ہیں، اور ان پٹ وولٹیج جیسے A اور B یا تو زیادہ یا کم ہو سکتے ہیں۔

اگر دونوں ان پٹ A اور B کم ہیں یا منطق 0، تو دونوں ڈایڈس متعصب ہو جائیں گے، اس طرح 'M' پر پوٹینشل ایک ڈائیوڈ کا وولٹیج ڈراپ ہے جو کہ 0.7 V ہے۔ اگرچہ 'Q' ٹرانجسٹر کو ترسیل میں چلانے کے لیے ، پھر ہمیں ڈائیوڈس D3، D4 اور 'Q' ٹرانجسٹر کے BE جنکشن کو آگے بڑھانے کے لیے 2.1 V کی ضرورت ہے، اس طرح یہ ٹرانزسٹر کٹ آف ہے اور Y = 1 آؤٹ پٹ فراہم کرتا ہے۔

Y = Vcc = منطق 1 اور A = B = 0 کے لئے، Y = 1 یا ہائی۔

اگر ان پٹ میں سے کوئی بھی A یا B کم ہے، تو ان پٹ میں سے کسی کو بھی +Vcc سے منسلک کسی بھی ٹرمینل کے ساتھ GND سے جوڑا جا سکتا ہے، مساوی ڈایڈڈ چلائے گا، اور VM ≅ 0.7 V & Q ٹرانزسٹر کاٹ دیا جائے گا۔ ، اور آؤٹ پٹ 'Y' = 1 یا منطق ہائی فراہم کریں۔

اگر A = 0 اور B =1 (یا) اگر A = 1 اور B = 0، تو آؤٹ پٹ Y = 1 یا HIGH۔

اگر دو ان پٹ جیسے A اور B دونوں ہائی ہیں اور دونوں A اور B صرف + Vcc سے جڑے ہوئے ہیں، تو D1 اور D2 دونوں ڈائیوڈ ریورس بیسڈ ہوں گے اور وہ چلتے نہیں ہیں۔ D3 اور D4 ڈائیوڈس فارورڈ بائیسڈ ہیں اور بیس ٹرمینل پر کرنٹ صرف Q ٹرانزسٹر کو Rd, D3 اور D4 کے ذریعے فراہم کیا جاتا ہے۔ ٹرانجسٹر کو سنترپتی میں چلایا جا سکتا ہے اور o/p وولٹیج کم وولٹیج ہو گا۔

A = B = 1 کے لیے، آؤٹ پٹ Y = 0 یا LOW۔

ترمیم شدہ ڈی ٹی ایل کی درخواستوں میں درج ذیل شامل ہیں۔

بعد میں آنے والے گیٹس کی منطق ہائی کنڈیشن کے ساتھ زیادہ رکاوٹ ہونے کی وجہ سے بڑا پنکھا نکلنا ممکن ہے۔ یہ سرکٹ اعلیٰ شور کی قوت مدافعت رکھتا ہے۔ ریزسٹرس اور کیپسیٹرز کے بجائے ایک سے زیادہ ڈائیوڈز کا استعمال اس سرکٹ کو مربوط سرکٹ کی شکل میں بہت زیادہ اقتصادی بنا دے گا۔

ڈائیوڈ ٹرانزسٹر لاجک اور نہ گیٹ

ڈائیوڈ ٹرانزسٹر لاجک NOR گیٹ ڈی ٹی ایل نینڈ گیٹ کی طرح ڈی آر ایل یا ٹرانزسٹر انورٹر والے گیٹ کے ساتھ ڈیزائن کیا گیا ہے۔ DTL NOR سرکٹس کو صرف ایک عام آؤٹ پٹ کے ذریعے مختلف DTL انورٹرز کو ملا کر زیادہ خوبصورتی سے ڈیزائن کیا جا سکتا ہے۔ اس طریقے سے، کئی انورٹرز کو NOR گیٹ کے لیے ضروری ان پٹ دینے کے لیے متحد کیا جا سکتا ہے۔

اس سرکٹ کو ڈی ٹی ایل انورٹر سرکٹ کے اجزاء کے ساتھ ڈیزائن کیا جا سکتا ہے۔ بجلی کی فراہمی اور دو 4.7 K مزاحم ، 1N914 یا 1N4148 سلکان ڈایڈس. نیچے دکھائے گئے سرکٹ کے مطابق سرکٹ کو جوڑیں۔

کام کرنا

کنکشن بنائے جانے کے بعد، سرکٹ کو بجلی کی فراہمی فراہم کرنے کی ضرورت ہے. اس کے بعد، ایک ڈپ سوئچ کے ساتھ پاور سپلائی سے A اور B میں چار ممکنہ ان پٹ کمبی نیشن لگائیں۔ اب ہر ان پٹ کے امتزاج کے لیے، آؤٹ پٹ 'Q' کی منطقی حالت کو نوٹ کرنے کی ضرورت ہے جیسا کہ ایل. ای. ڈی اور اس آؤٹ پٹ کو ریکارڈ کریں۔ NOR گیٹ آپریشن کے ساتھ نتائج کا موازنہ کریں۔ ایک بار جب آپ اپنے مشاہدات مکمل کر لیں، تو بجلی کی فراہمی بند کر دیں۔

|

اے |

بی |

Y = (A+B)' |

|

0 |

0 | 1 |

|

0 |

1 | 0 |

| 1 | 0 |

0 |

| 1 | 1 |

0 |

ڈائیوڈ ٹرانزسٹر لاجک اور گیٹ

ڈائیوڈ ٹرانزسٹر لاجک اور گیٹ نیچے دکھایا گیا ہے۔ اس سرکٹ میں، منطق بیان کرتی ہے جیسے؛ 1 اور 0 کو اسی طرح +5V مثبت منطق اور 0V کے طور پر لیا جاتا ہے۔

جب بھی A1، A2 (یا) A3 سے کوئی بھی ان پٹ کم منطقی حالت میں ہوتا ہے تو اس ان پٹ سے منسلک ڈایڈڈ فارورڈ بائیس میں ہوگا اس کے بعد ٹرانزسٹر کٹ آف میں آجائے گا اور آؤٹ پٹ LOW یا logic 0 ہوگا۔ اسی طرح، اگر تینوں ان پٹ منطق 1 پر ہیں تو پھر کوئی بھی ڈائیوڈ کنڈکٹ اور ٹرانزسٹر بھاری بھرکم نہیں کرتا ہے۔ اس کے بعد، ٹرانزسٹر سیر ہو جاتا ہے اور آؤٹ پٹ ہائی یا منطق 1 ہو گا۔

ڈایڈڈ ٹرانجسٹر لاجک اور گیٹ کا سچ ٹیبل نیچے دکھایا گیا ہے۔

|

A1 |

A2 | A3 |

Y = A.B |

|

0 |

0 | 0 | 0 |

|

0 |

0 | 1 | 0 |

|

0 |

1 | 0 |

0 |

| 0 | 1 | 1 |

0 |

|

1 |

0 | 0 | 0 |

|

1 |

0 | 1 |

0 |

| 1 | 1 | 0 |

0 |

| 1 | 1 | 1 |

1 |

ڈی ٹی ایل، ٹی ٹی ایل اور آر ٹی ایل کے درمیان موازنہ

ڈی ٹی ایل، ٹی ٹی ایل، اور آر ٹی ایل کے درمیان فرق ذیل میں زیر بحث آئے ہیں۔

| ڈی ٹی ایل | ٹی ٹی ایل |

RTL |

| ڈی ٹی ایل کی اصطلاح کا مطلب ڈائیوڈ-ٹرانسسٹر لاجک ہے۔ | ٹی ٹی ایل کی اصطلاح کا مطلب ٹرانزسٹر-ٹرانسسٹر لاجک ہے۔ | RTL کی اصطلاح کا مطلب ہے Resistor-Transistor Logic۔ |

| DTL میں، منطقی دروازے PN جنکشن ڈائیوڈس اور ٹرانزسٹرز کے ساتھ ڈیزائن کیے گئے ہیں۔ | TTL میں، منطقی دروازے BJTs کے ساتھ ڈیزائن کیے گئے ہیں۔

|

RTL میں، لاجک گیٹس کو ریزسٹر اور ٹرانزسٹر کے ساتھ ڈیزائن کیا گیا ہے۔ |

| ڈی ٹی ایل میں، ڈائیوڈز کو i/p اجزاء کے طور پر استعمال کیا جاتا ہے اور ٹرانزسٹر کو o/p اجزاء کے طور پر استعمال کیا جاتا ہے۔ | ٹی ٹی ایل میں، ایک ٹرانجسٹر کو بڑھانے کے لیے استعمال کیا جاتا ہے جبکہ دوسرا ٹرانزسٹر سوئچنگ کے مقاصد کے لیے استعمال ہوتا ہے۔ | RTL میں ریزسٹر کو i/p جزو کے طور پر استعمال کیا جاتا ہے اور ٹرانزسٹر کو o/p جزو کے طور پر استعمال کیا جاتا ہے۔ |

| RTL کے مقابلے میں DTL جواب بہتر ہے۔ | TTL ردعمل DTL اور RTL سے بہت بہتر ہے۔ | RTL جواب سست ہے۔ |

| بجلی کا نقصان کم ہے۔ | اس میں بجلی کا بہت کم نقصان ہے۔ | بجلی کا نقصان زیادہ ہے۔ |

| اس کی تعمیر پیچیدہ ہے۔ | اس کی تعمیر بہت آسان ہے۔ | اس کی تعمیر سادہ ہے۔ |

| ڈی ٹی ایل کم از کم فین آؤٹ 8 ہے۔ | ٹی ٹی ایل کم از کم فین آؤٹ 10 ہے۔ | RTL کم از کم فین آؤٹ 5 ہے۔ |

| ہر دروازے کے لیے بجلی کی کھپت عام طور پر 8 سے 12 میگاواٹ ہوتی ہے۔ | ہر دروازے کے لیے بجلی کی کھپت عام طور پر 12 سے 22 میگاواٹ ہوتی ہے۔ | ہر دروازے کے لیے بجلی کی کھپت عام طور پر 12 میگاواٹ ہوتی ہے۔ |

| اس کی شور کی قوت مدافعت اچھی ہے۔ | اس کی شور کی قوت مدافعت بہت اچھی ہے۔ | اس کی شور کی قوت مدافعت درمیانی ہے۔ |

| گیٹ کے لیے اس کی عام تبلیغ میں تاخیر 30 این ایس ہے۔ | گیٹ کے لیے اس کی عام پھیلاؤ کی تاخیر 12 سے 6 این ایس ہے۔ | گیٹ کے لیے اس کی عام تبلیغ میں تاخیر 12 این ایس ہے۔ |

| اس کی کلاک ریٹ 12 سے 30 میگا ہرٹز ہے۔ | اس کی گھڑی کی شرح 15 سے 60 میگا ہرٹز ہے۔ | اس کی کلاک ریٹ 8 میگا ہرٹز ہے۔ |

| اس میں کافی تعداد میں افعال ہیں۔ | اس میں بہت زیادہ تعداد میں افعال ہیں۔ | اس کے افعال کی ایک بڑی تعداد ہے۔ |

| ڈی ٹی ایل منطق بنیادی سوئچنگ اور ڈیجیٹل سرکٹس میں استعمال ہوتی ہے۔ | ٹی ٹی ایل منطق جدید ڈیجیٹل سرکٹس اور انٹیگریٹڈ سرکٹس میں استعمال ہوتی ہے۔ | RTL پرانے کمپیوٹرز میں استعمال ہوتا ہے۔ |

فوائد

ڈائیوڈ ٹرانزسٹر لاجک سرکٹ کے فوائد میں درج ذیل شامل ہیں۔

- DTL کی سوئچنگ کی رفتار RTL کے مقابلے میں تیز ہے۔

- ڈی ٹی ایل سرکٹس کے اندر ڈایڈس کا استعمال انہیں سستا بناتا ہے کیونکہ ICs پر ڈایڈس کی فیبریکیشن ریزسٹرس اور کیپسیٹرز کے مقابلے میں آسان ہے۔

- ڈی ٹی ایل سرکٹس کے اندر بجلی کا نقصان بہت کم ہے۔

- ڈی ٹی ایل سرکٹس میں تیزی سے سوئچنگ کی رفتار ہوتی ہے۔

- DTL میں زیادہ فین آؤٹ اور بہتر شور مارجن ہے۔

دی ڈایڈڈ ٹرانجسٹر لاجک سرکٹس کے نقصانات مندرجہ ذیل شامل ہیں.

- ٹی ٹی ایل کے مقابلے ڈی ٹی ایل کی آپریٹنگ اسپیڈ کم ہے۔

- اس میں گیٹ کے پھیلاؤ میں بہت بڑی تاخیر ہے۔

- زیادہ ان پٹ کے لیے، ڈی ٹی ایل کا آؤٹ پٹ سنترپتی میں جاتا ہے۔

- یہ پورے آپریشن میں گرمی پیدا کرتا ہے۔

درخواستیں

دی ڈایڈڈ ٹرانجسٹر لاجک کی ایپلی کیشنز مندرجہ ذیل شامل ہیں.

- Diode- ٹرانزسٹر لاجک کا استعمال ڈیجیٹل سرکٹس کو ڈیزائن اور فیبریکیٹ کرنے کے لیے کیا جاتا ہے۔ منطق کے دروازے ان پٹ اسٹیج کے اندر ڈائیوڈز اور آؤٹ پٹ اسٹیج پر BJTs استعمال کریں۔

- ڈی ٹی ایل ایک مخصوص قسم کا سرکٹ ہے جو موجودہ ڈیجیٹل الیکٹرانکس میں برقی سگنلز کی کارروائی کے لیے استعمال ہوتا ہے۔

- ڈی ٹی ایل کو سادہ منطقی سرکٹس بنانے کے لیے استعمال کیا جاتا ہے۔

اس طرح، یہ ہے ڈایڈڈ ٹرانجسٹر منطق کا ایک جائزہ ، سرکٹ، کام کرنے، فوائد، نقصانات، اور ایپلی کیشنز۔ RTL سرکٹس کے مقابلے میں DTL سرکٹس زیادہ پیچیدہ ہیں، لیکن اس منطق نے RTL کو اس کی اعلیٰ FAN OUT صلاحیت اور بہتر شور مارجن کی وجہ سے بدل دیا ہے لیکن DTL کی رفتار سست ہے۔ یہاں آپ کے لیے ایک سوال ہے، RTL کیا ہے؟