RISC V ایک انسٹرکشن سیٹ آرکیٹیکچر ہے جسے یونیورسٹی آف کیلیفورنیا، برکلے نے تیار کیا ہے۔ RISC کا تصور اس حقیقت سے متاثر ہوا کہ پروسیسر کی زیادہ تر ہدایات زیادہ تر کمپیوٹر پروگراموں کے ذریعہ استعمال نہیں کی گئیں۔ لہذا، کے ڈیزائن میں غیر ضروری ضابطہ کشائی کی منطق کا استعمال کیا جا رہا تھا۔ پروسیسرز , زیادہ بجلی کے ساتھ ساتھ علاقے کا استعمال. ہدایات کے سیٹ کو مختصر کرنے اور رجسٹر وسائل کے اندر مزید سرمایہ کاری کرنے کے لیے، RISC V پروسیسر لاگو کیا گیا تھا.

اس ٹیکنالوجی کو بہت سے ٹیک جنات اور اسٹارٹ اپس نے دیکھا کیونکہ یہ مکمل طور پر اوپن سورس اور مفت ہے۔ پروسیسر کی زیادہ تر اقسام لائسنس کے معاہدے کے ساتھ دستیاب ہیں، تاہم اس قسم کے پروسیسر کے ساتھ؛ کوئی بھی اپنے نئے پروسیسر ڈیزائن بنا سکتا ہے۔ لہذا یہ مضمون RISC V پروسیسر - کام کرنے اور اس کی ایپلی کیشنز کے ایک جائزہ پر بحث کرتا ہے۔

RISC V پروسیسر کیا ہے؟

RISC V پروسیسر میں، RISC کا مطلب ہے 'کم انسٹرکشن سیٹ کمپیوٹر' جو کمپیوٹر کی چند ہدایات پر عمل کرتا ہے جبکہ 'V' کا مطلب 5 ویں نسل ہے۔ یہ ایک اوپن سورس ہارڈویئر ISA (انسٹرکشن سیٹ آرکیٹیکچر) کے قائم کردہ اصول پر مبنی ہے۔ خطرہ .

دیگر ISA ڈیزائنوں کے مقابلے میں، یہ ISA اوپن سورس لائسنس کے ساتھ دستیاب ہے۔ لہذا، متعدد مینوفیکچرنگ کمپنیوں نے اعلان کیا ہے اور اوپن سورس آپریٹنگ سسٹم کے ساتھ RISC-V ہارڈویئر بھی فراہم کیا ہے۔

یہ ایک نیا فن تعمیر ہے اور یہ کھلے، غیر محدود اور مفت لائسنسوں میں دستیاب ہے۔ اس پروسیسر کو چپ اور ڈیوائس بنانے والی صنعتوں کی جانب سے وسیع تعاون حاصل ہے۔ لہذا یہ بنیادی طور پر بہت ساری ایپلی کیشنز میں استعمال کرنے کے لئے آزادانہ طور پر قابل توسیع اور مرضی کے مطابق ڈیزائن کیا گیا ہے۔

RISC V تاریخ

RISC کی ایجاد پروفیسر ڈیوڈ پیٹرسن نے 1980 کے قریب یونیورسٹی آف کیلیفورنیا، برکلے میں کی تھی۔ پروفیسر ڈیوڈ نے پروفیسر جان ہینیسی کے ساتھ اپنی کوششیں دو کتابوں میں پیش کیں جن میں 'کمپیوٹر آرگنائزیشن اینڈ ڈیزائن' اور 'اسٹینفورڈ یونیورسٹی میں کمپیوٹر آرکیٹیکچر' ہے۔ لہذا، انہوں نے ACM A.M. سال 2017 میں ٹورنگ ایوارڈ۔

سال 1980 سے 2010 سال تک، RISC پانچویں نسل کی ترقی کی تحقیق شروع کی گئی اور آخر کار اس کی شناخت RISC-V کے نام سے ہوئی جسے خطرہ پانچ کہا جاتا ہے۔

RISC V آرکیٹیکچر اینڈ ورکنگ

RV12 RISC V فن تعمیر ذیل میں دکھایا گیا ہے۔ RV12 سنگل کور RV32I اور RV64I کے مطابق RISC CPU کے ساتھ انتہائی قابل ترتیب ہے جو ایمبیڈڈ فیلڈز میں استعمال ہوتا ہے۔ RV12 صنعتی معیاری RISC-V انسٹرکشن سیٹ کے لحاظ سے 32 یا 64-bit CPU فیملی سے بھی ہے۔

آر وی 12 صرف ایک ہارورڈ فن تعمیر کو ہدایت کے ساتھ ساتھ ڈیٹا میموری تک بیک وقت رسائی کے لیے انجام دیتا ہے۔ اس میں 6-اسٹیج پائپ لائن بھی شامل ہے جو کارکردگی کو بہتر بنانے کے لیے عمل کے درمیان اوورلیپ کے ساتھ ساتھ میموری تک رسائی کو بہتر بنانے میں مدد کرتی ہے۔ اس فن تعمیر میں بنیادی طور پر برانچ پریڈیکشن، ڈیٹا کیش، ڈیبگ یونٹ، انسٹرکشن کیشے، اور اختیاری ملٹیپلائر یا ڈیوائیڈر یونٹس شامل ہیں۔

RV12 RISC V کی اہم خصوصیات میں درج ذیل شامل ہیں۔

- یہ انڈسٹری کا معیاری انسٹرکشن سیٹ ہے۔

- 32 یا 64 بٹ ڈیٹا کے ساتھ پیرامیٹرائزڈ۔

- اس میں عین مطابق اور تیز مداخلتیں ہیں۔

- حسب ضرورت ہدایات ملکیتی ہارڈویئر ایکسلریٹر کے اضافے کی اجازت دیتی ہیں۔

- سنگل سائیکل کا نفاذ۔

- فولڈ کو بہتر بنانے کے ساتھ چھ مرحلے والی پائپ لائن۔

- میموری پروٹیکشن کے ساتھ سپورٹ۔

- اختیاری یا پیرامیٹرائزڈ کیشز۔

- انتہائی پیرامیٹرائزڈ۔

- صارفین 32/64 بٹ ڈیٹا اور برانچ پریڈیکشن یونٹ منتخب کر سکتے ہیں۔

- صارفین ہدایات/ڈیٹا کیشز کو منتخب کر سکتے ہیں۔

- صارف کے قابل انتخاب ساخت، سائز اور کیشے کا فن تعمیر۔

- ہارڈ ویئر ڈیوائیڈر یا ملٹیپلر سپورٹ صارف کی طرف سے طے شدہ تاخیر سے۔

- بس کا فن تعمیر لچکدار ہے جو Wishbone اور AHB کو سپورٹ کرتا ہے۔

- یہ ڈیزائن طاقت اور سائز کو بہتر بناتا ہے۔

- ڈیزائن مکمل طور پر پیرامیٹرائزڈ ہے جو کارکردگی یا پاور ٹریڈ آف فراہم کرتا ہے۔

- طاقت کو کم کرنے کے لیے گیٹڈ CLK ڈیزائن۔

- صنعت کے معیار کے مطابق سافٹ ویئر سپورٹ۔

- آرکیٹیکچرل سمیلیٹر۔

- Eclipse IDE لینکس/ونڈوز کے لیے استعمال ہوتا ہے۔

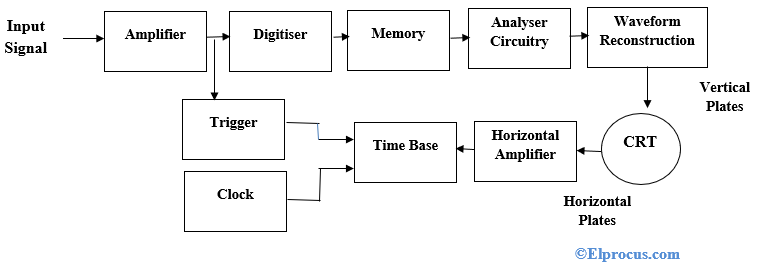

RISC V ایگزیکیوشن پائپ لائن

اس میں پانچ مراحل شامل ہیں جیسے IF (انسٹرکشن فیچ)، آئی ڈی (انسٹرکشن ڈی کوڈ)، EX (ایکسکیوٹ)، ایم ای ایم (میموری تک رسائی) اور ڈبلیو بی (رجسٹر رائٹ بیک)۔

ہدایات کی بازیافت

انسٹرکشن فیچ یا IF مرحلے میں، پروگرام کاؤنٹر (PC) اور انسٹرکشن میموری سے ایک ہی انسٹرکشن پڑھی جاتی ہے جسے اگلی ہدایات میں اپ ڈیٹ کیا جاتا ہے۔

ہدایات پری ڈی کوڈ

ایک بار جب RVC سپورٹ کی اجازت ہو جاتی ہے، تو انسٹرکشن پری ڈیکوڈ مرحلہ 16-بٹ-کمپریسڈ انسٹرکشن کو مقامی 32-بٹ انسٹرکشن میں ڈی کوڈ کر دے گا۔

انسٹرکشن ڈی کوڈ

انسٹرکشن ڈی کوڈ (ID) مرحلے میں، رجسٹر فائل کی اجازت ہے اور بائی پاس کنٹرولز کا فیصلہ کیا جاتا ہے۔

پھانسی

ایگزیکیوٹ مرحلے میں، نتیجہ کا حساب ALU، DIV، MUL انسٹرکشن کے لیے کیا جاتا ہے، اسٹور یا لوڈ انسٹرکشن کے لیے اجازت دی گئی میموری، اور شاخوں اور چھلانگوں کو ان کے متوقع نتائج سے ماپا جاتا ہے۔

یاداشت

میموری کے اس مرحلے میں پائپ لائن کے ذریعے میموری تک رسائی حاصل کی جاتی ہے۔ اس مرحلے کی شمولیت پائپ لائن کی اعلیٰ کارکردگی کو یقینی بناتی ہے۔

واپس لکھیں۔

اس مرحلے میں، عمل درآمد کے مرحلے کا نتیجہ رجسٹر فائل میں لکھا جاتا ہے۔

برانچ پیشن گوئی کرنے والا

اس پروسیسر میں برانچ پریڈیکٹر یونٹ یا BPU شامل ہے جو کہ RISC V پروسیسر کی رہنمائی کرنے کے لیے ماضی کے ڈیٹا کو ذخیرہ کرنے کے لیے استعمال کیا جاتا ہے تاکہ یہ فیصلہ کیا جا سکے کہ آیا کوئی مخصوص برانچ لیا گیا ہے یا نہیں۔ یہ پیشن گوئی کرنے والے ڈیٹا کو صرف ایک بار اپ ڈیٹ کیا جاتا ہے جب برانچ کے عمل میں آتا ہے۔

اس یونٹ میں مختلف پیرامیٹرز شامل ہیں جو اس کے رویے کا تعین کرتے ہیں۔ مثال کے طور پر، HAS_BPU کا استعمال اس بات کا تعین کرنے کے لیے کیا جاتا ہے کہ آیا کوئی برانچ پیش گوئی کرتی ہے کہ کوئی یونٹ موجود ہے، BPU_GLOBAL_BITS اس بات کا تعین کرے گا کہ ماضی کے کتنے بٹس استعمال کیے جائیں اور BPU_LOCAL_BITS اس بات کا تعین کرے گا کہ پروگرام کاؤنٹر کے کتنے LSB استعمال کیے جائیں۔ BPU_LOCAL_BITS اور BPU_GLOBAL_BITS کا مجموعہ ایک ویکٹر بنائے گا جو بنیادی طور پر برانچ-پیش گوئی-ٹیبل کو حل کرنے کے لیے استعمال ہوتا ہے۔

ڈیٹا کیش

یہ بنیادی طور پر میموری کے نئے رسائی والے مقامات کو بفر کرکے ڈیٹا میموری تک رسائی کو تیز کرنے کے لیے استعمال ہوتا ہے۔ یہ نصف لفظ، بائٹ اور لفظ تک رسائی کو سنبھالنے کے قابل ہے جب XLEN = 32 اگر وہ اپنی حدود میں ہوں۔ یہ آدھے لفظ، بائٹ، لفظ اور دوہرے لفظ تک رسائی کو سنبھالنے کے قابل بھی ہے جب XLEN=64 اگر وہ اپنی حدود میں ہوں۔

کیش مس کے دوران، ایک مکمل بلاک کو میموری پر واپس لکھا جا سکتا ہے، لہذا اگر ضروری ہو تو، کیش میں ایک نیا بلاک لوڈ کیا جا سکتا ہے۔ DCACHE_SIZE کو صفر پر سیٹ کر کے ڈیٹا کیش کو غیر فعال کر دیا گیا ہے۔ اس کے بعد، میموری کے مقامات تک براہ راست رسائی حاصل کی جاتی ہے۔ ڈیٹا انٹرفیس .

انسٹرکشن کیشے

یہ بنیادی طور پر نئی لائی گئی ہدایات کو بفر کرکے ہدایات کی بازیافت کو تیز کرنے کے لیے استعمال کیا جاتا ہے۔ یہ کیش کسی بھی 16 بٹ باؤنڈری پر ہر سائیکل کے لیے ایک پارسل لانے کے لیے استعمال کیا جاتا ہے لیکن بلاک باؤنڈری کے پار نہیں۔ کیش مس کے دوران، انسٹرکشن میموری سے ایک پورا بلاک لوڈ کیا جا سکتا ہے۔ اس کیش کی ترتیب صارف کی ضروریات کی بنیاد پر کی جا سکتی ہے۔ کیشے کا سائز، متبادل الگورتھم، اور بلاک کی لمبائی قابل ترتیب ہے۔

ICACHE_SIZE کو صفر پر سیٹ کر کے انسٹرکشن سائیکل کو غیر فعال کر دیا جائے گا۔ اس کے بعد، پارسل براہ راست میموری سے حاصل کیے جاتے ہیں۔ انسٹرکشن انٹرفیس۔

ڈیبگ یونٹ

ڈیبگ یونٹ ڈیبگ ماحول کو روکنے اور CPU کی جانچ کرنے کی اجازت دے گا۔ اس کی اہم خصوصیات ہیں برانچ ٹریسنگ، سنگل سٹیپ ٹریسنگ تک 8- ہارڈ ویئر بریک پوائنٹس۔

فائل رجسٹر کریں۔

یہ X0 سے X31 تک 32 رجسٹر مقامات کے ساتھ ڈیزائن کیا گیا ہے جہاں X9 رجسٹر ہمیشہ صفر ہوتا ہے۔ رجسٹر فائل میں 1- رائٹ پورٹ اور 2- ریڈ پورٹ شامل ہیں۔

قابل ترتیب انٹرفیس

یہ ایک بیرونی انٹرفیس ہے جہاں یہ پروسیسر مختلف بیرونی بس انٹرفیس کو سپورٹ کرتا ہے۔

RISC V کیسے کام کرتا ہے؟

RISC-V ایک انسٹرکشن سیٹ آرکیٹیکچر ہے جس کی جڑیں RISC (کم انسٹرکشن سیٹ کمپیوٹر) کے اصولوں کے اندر ہے۔ یہ پروسیسر بہت منفرد اور انقلابی بھی ہے کیونکہ یہ ایک مفت، عام اور اوپن سورس ISA ہے جہاں ہارڈ ویئر تیار کیا جا سکتا ہے، سافٹ ویئر کو پورٹ کیا جا سکتا ہے اور پروسیسر اس کی مدد کے لیے ڈیزائن کیے جا سکتے ہیں۔

فرق B/W RISC V بمقابلہ MIPS

RISC V اور MIPS کے درمیان فرق میں درج ذیل شامل ہیں۔

|

RISC V |

ایم آئی پی ایس |

| RISC V کا مطلب ہے Redued Instruction Set Computer جہاں 'V' پانچویں جنریشن ہے۔ | اصطلاح 'MIPS' کا مطلب ہے 'ملین ہدایات فی سیکنڈ'۔ |

| RISC-V چھوٹے آلات کے مینوفیکچررز کو بغیر ادائیگی کے ہارڈ ویئر ڈیزائن کرنے کی اجازت دیتا ہے۔ | MIPS مینوفیکچرر کو ادائیگی کرکے پروسیسر کی رفتار کی پیمائش کرنے کی اجازت دیتا ہے کیونکہ یہ مفت نہیں ہے۔ |

| MIPS مؤثر طریقے سے مر گیا ہے۔ | RISC-V مؤثر طریقے سے مردہ نہیں ہے۔ |

| یہ پروسیسر دو رجسٹروں کا موازنہ کرنے کے لیے برانچ ہدایات فراہم کرتا ہے۔ | MIPS کا انحصار تقابل کی ہدایت پر ہے جو 1 یا 0 کے رجسٹر کا پتہ لگاتا ہے اس بنیاد پر کہ آیا کنٹراسٹ درست ہے۔ |

| ISA انکوڈنگ سکیم RISC V میں فکسڈ اور متغیر ہے۔ | ISA انکوڈنگ سکیم MIPS میں طے شدہ ہے۔ |

| انسٹرکشن سیٹ کا سائز 16 بٹ یا 32 بٹ یا 64 بٹ یا 128 بٹ ہے۔ | انسٹرکشن سیٹ کا سائز 32 بٹ یا 64 بٹ ہے۔ |

| اس میں 32 عمومی مقصد اور فلوٹنگ پوائنٹ رجسٹر ہیں۔ | اس میں 31 عمومی مقصد اور فلوٹنگ پوائنٹ رجسٹر ہیں۔ |

| اس میں 26 سنگل اور ڈبل پریسجن فلوٹنگ پوائنٹ آپریشنز ہیں۔ | اس میں 15 سنگل اور ڈبل پریزین فلوٹنگ پوائنٹ آپریشنز ہیں۔ |

فرق B/W RISC V بمقابلہ ARM

RISC Vs ARM کے درمیان فرق میں درج ذیل شامل ہیں۔

|

RISC V |

بازو |

| RISC-V اوپن سورس ہے، اس لیے اسے کسی لائسنس کی ضرورت نہیں ہے۔ | ARM ایک بند ذریعہ ہے، لہذا اسے لائسنس کی ضرورت ہے۔ |

| یہ ایک نیا پروسیسر پلیٹ فارم ہے، اس لیے سافٹ ویئر اور پروگرامنگ ماحول کے لیے بہت کم سپورٹ ہے۔ | اے آر ایم کی ایک بہت بڑی آن لائن کمیونٹی ہے، جو مائیکرو پروسیسرز، مائیکرو کنٹرولرز اور سرورز جیسے مختلف پلیٹ فارمز میں ہدف ڈیزائنرز کی مدد کے لیے لائبریریوں اور ڈھانچے کو سپورٹ کرتی ہے۔ |

| RISC V پر مبنی چپس 1 واٹ پاور استعمال کرتی ہیں۔ | ARM پر مبنی چپس 4 واٹ سے کم پاور استعمال کرتی ہیں۔ |

| اس میں ایک مقررہ اور متغیر ISA انکوڈنگ سسٹم ہے۔ | اس میں ایک مقررہ ISA انکوڈنگ سسٹم ہے۔ |

| RISC V انسٹرکشن سیٹ کا سائز 16-bit سے 128-bit تک ہوتا ہے۔ | اس کی ہدایات کا سائز 16 بٹ سے 64 بٹ تک ہے۔ |

| اس میں 32 عام مقصد اور فلوٹنگ پوائنٹ رجسٹر شامل ہیں۔ | اس میں 31 عام مقصد اور فلوٹنگ پوائنٹ رجسٹر شامل ہیں۔ |

| اس میں 26 سنگل پریزین فلوٹنگ پوائنٹ آپریشنز ہیں۔ | اس میں 33 سنگل پریزین فلوٹنگ پوائنٹ آپریشنز ہیں۔ |

| اس میں 26 ڈبل پریسجن فلوٹنگ پوائنٹ آپریشنز ہیں۔ | اس میں 29 ڈبل پریسجن فلوٹنگ پوائنٹ آپریشنز ہیں۔ |

RISC V Verilog کوڈ

RISC کے لیے انسٹرکشن میموری ویری لاگ کوڈ ذیل میں دکھایا گیا ہے۔

// RISC پروسیسر کے لیے ویری لاگ کوڈ

// انسٹرکشن میموری کے لیے ویری لاگ کوڈ

ماڈیول انسٹرکشن_میموری(

ان پٹ [15:0] پی سی،

آؤٹ پٹ [15:0] ہدایات

);

reg [`col – 1:0] میموری [`row_i – 1:0]؛

تار [3 : 0] rom_addr = pc[4 : 1]؛

ابتدائی

شروع

$readmemb(“./test/test.prog”, memory,0,14);

اختتام

تفویض ہدایات = میموری [rom_addr]؛

endmodule

16 بٹ RISC V پروسیسر کے لیے ویری لاگ کوڈ:

ماڈیول Risc_16_bit(

ان پٹ clk

);

وائر جمپ،بنی،بیق،میم_ریڈ،میم_لائٹ،ایلو_ایس آر سی،ریگ_ڈی ایس ٹی،میم_ٹو_ریگ،ریگ_لائٹ؛

تار [1:0] alu_op؛

تار [3:0] اوپکوڈ؛

// ڈیٹا پاتھ

Datapath_Unit DU

(

clk(clk)،

.jump(چھلانگ)،

.frog(مینڈک)،

.mem_read(میم_پڑھیں)،

.mem_write(mem_write)،

.alu_src(alu_src)،

.reg_dst(reg_dst)،

.mem_to_reg(mem_to_reg)،

.reg_write(reg_write)،

.bne(bne)،

.alu_op(alu_op)،

.opcode(opcode)

);

// کنٹرول یونٹ

کنٹرول_یونٹ کنٹرول

(

.opcode(opcode)،

.reg_dst(reg_dst)،

.mem_to_reg(mem_to_reg)،

.alu_op(alu_op)،

.jump(چھلانگ)،

.bne(bne)،

.frog(مینڈک)،

.mem_read(میم_پڑھیں)،

.mem_write(mem_write)،

.alu_src(alu_src)،

.reg_write(reg_write)

);

endmodule

انسٹرکشن سیٹ

RISC V ہدایات کے سیٹوں پر ذیل میں تبادلہ خیال کیا گیا ہے۔

ریاضی کے آپریشنز

RISC V ریاضی کی کارروائیاں ذیل میں درج ہیں۔

| یادداشت کا | قسم | ہدایت | تفصیل |

| rd, rs1, rs2 شامل کریں۔ |

آر |

شامل کریں۔ | rdß rs1 + rs2 |

| SUB rd, rs1, rs2 |

آر |

گھٹائیں | rdß rs1 – rs2 |

| ADDI rd, rs1, imm12 |

میں |

فوری طور پر شامل کریں۔ | rdß rs1 + imm12 |

| SLT rd, rs1, rs2 |

آر |

سے کم سیٹ کریں۔ | rdß rs1 -< rs2 |

| SLTI rd, rs1, imm12 |

میں |

فوری سے کم سیٹ کریں۔ | rdß rs1 -< imm12 |

| SLTU rd, rs1, rs2 |

آر |

غیر دستخط شدہ سے کم سیٹ کریں۔ | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

میں |

فوری طور پر غیر دستخط شدہ سے کم سیٹ کریں۔ | rdß rs1 -< imm12 |

| LUI rd, imm20 |

میں |

اوپری کو فوری طور پر لوڈ کریں۔ | rdß imm20<<12 |

| AUIP rd, imm20 |

میں |

پی سی میں فوری طور پر اوپری شامل کریں۔ | rdß PC+imm20<<12 |

منطقی آپریشنز

RISC V منطقی کارروائیاں ذیل میں درج ہیں۔

| یادداشت کا | قسم | ہدایت | تفصیل |

| اور rd, rs1, rs2 |

آر |

اور | rdß rs1 اور rs2 |

| یا rd، rs1، rs2 |

آر |

یا | rdß rs1 | rs2 |

| XOR rd, rs1, rs2 |

آر |

مفت | rdß rs1 ^ rs2 |

| ANDI rd, rs1, imm12 |

میں |

اور فوری | rdß rs1 اور imm2 |

| ORI rd, rs1, imm12 |

میں |

یا فوری | rdß rs1 | imm12 |

| OXRI rd, rs1, imm12 |

میں |

XOR فوری | rdß rs1 ^ rs2 |

| ایس ایل ایل آر ڈی، آر ایس 1، آر ایس 2 |

آر |

منطقی بائیں طرف شفٹ کریں۔ | rdß rs1 << rs2 |

| SRL rd, rs1, rs2 |

آر |

دائیں منطقی شفٹ کریں۔ | rdß rs1 >> rs2 |

| RAS rd, rs1, rs2 |

آر |

دائیں ریاضی کو شفٹ کریں۔ | rdß rs1 >> rs2 |

| SLLI rd, rs1, shamt |

میں |

فوری طور پر منطقی بائیں طرف شفٹ کریں۔ | rdß rs1 << shamt |

| SRLI rd, rs1, shamt |

میں |

دائیں منطقی فوری طور پر شفٹ کریں۔ | rdß rs1 >> shamt |

| SRAI rd, rs1, shamt |

میں |

دائیں ریاضی کو فوری طور پر شفٹ کریں۔ | rdß rs1 >> shamt |

لوڈ/اسٹور آپریشنز

RISC V لوڈ/اسٹور آپریشنز ذیل میں درج ہیں۔

| یادداشت کا | قسم | ہدایت | تفصیل |

| LD rd, imm12 (rs1) |

میں |

ڈبل ورڈ لوڈ کریں۔ | rdß mem [rs1 +imm12] |

| LW rd, imm12 (rs1) |

میں |

لفظ لوڈ کریں۔ | rdß mem [rs1 +imm12] |

| LH rd, imm12 (rs1) |

میں |

آدھے راستے پر لوڈ کریں۔ | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

میں |

لوڈ بائٹ | rdß mem [rs1 +imm12] |

| LWU rd, imm12 (rs1) |

میں |

غیر دستخط شدہ لفظ لوڈ کریں۔ | rdß mem [rs1 +imm12] |

| LHU rd, imm12 (rs1) |

میں |

آدھا لفظ غیر دستخط شدہ لوڈ کریں۔ | rdß mem [rs1 +imm12] |

| LBU rd, imm12 (rs1) |

میں |

لوڈ بائٹ غیر دستخط شدہ | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

ایس |

ڈبل لفظ ذخیرہ کریں۔ | rs2 to mem [rs1 +imm12] |

| SW rs2, imm12 (rs1) |

ایس |

ذخیرہ الفاظ | rs2 (31:0) to mem [rs1 +imm12] |

| SH rs2, imm12 (rs1) |

ایس |

آدھے راستے پر اسٹور کریں۔ | rs2 (15:0) to mem [rs1 +imm12] |

| SB rs2, imm12 (rs1) |

ایس |

اسٹور بائٹ | rs2 (15:0) to mem [rs1 +imm12] |

| SRAI rd, rs1, shamt |

میں |

دائیں ریاضی کو فوری طور پر شفٹ کریں۔ | rs2 (7:0) to mem [rs1 +imm12] |

برانچنگ آپریشنز

RISC V برانچنگ آپریشنز ذیل میں درج ہیں۔

| یادداشت کا | قسم | ہدایت | تفصیل |

| BEQ rs1, rs2, imm12 |

ایس بی |

برانچ برابر | اگر rs1== rs2 PC ß PC+im12 |

| BNE rs1، rs2، imm12 |

ایس بی |

برانچ برابر نہیں ہے۔ | اگر rs1!= rs2 PC ß PC+im12 |

| BGE rs1, rs2, imm12 |

ایس بی |

اس سے بڑی یا برابر شاخ | اگر rs1>= rs2 PC ß PC+im12 |

| BGEU rs1, rs2, imm12 |

ایس بی |

غیر دستخط شدہ سے زیادہ یا اس کے برابر برانچ | اگر rs1>= rs2 PC ß PC+im12 |

| BLT rs1, rs2, imm12 |

ایس بی |

سے کم برانچ | اگر rs1< rs2 PC ß PC+im12 |

| BLTU rs1, rs2, imm12 |

ایس بی |

سے کم برانچ غیر دستخط شدہ | اگر rs1< rs2 PC ß PC+im12 <<1 |

| JAL rd, imm20 |

یو جے |

چھلانگ لگائیں اور لنک کریں۔ | rdßPC+4 PCß PC+imm20 |

| JALR rd, imm12(rs1) |

میں |

چھلانگ لگائیں اور لنک رجسٹر کریں۔ | rdßPC+4 PCß rs1+imm12 |

فوائد

دی RISC کے فوائد وی پروسیسر مندرجہ ذیل شامل ہیں.

- RISCV استعمال کرکے، ہم ترقی کا وقت، سافٹ ویئر کی ترقی، تصدیق وغیرہ کو بچا سکتے ہیں۔

- اس پروسیسر میں سادگی، کشادگی، ماڈیولریٹی، کلین سلیٹ ڈیزائن، اور توسیع پذیری جیسے بہت سے فوائد ہیں۔

- اس کی حمایت کئی زبانوں کے کمپائلرز جیسے GCC (GNU Compiler Collection)، ایک مفت سافٹ ویئر کمپائلر اور لینکس OS .

- بغیر کسی رائلٹی، لائسنسنگ فیس اور کوئی تار منسلک نہ ہونے کی وجہ سے کمپنیاں اسے آزادانہ طور پر استعمال کر سکتی ہیں۔

- RISC-V پروسیسر میں کوئی نئی یا اختراعی خصوصیات شامل نہیں ہیں کیونکہ یہ صرف RISC کے قائم کردہ اصولوں کی پیروی کرتا ہے۔

- کئی دیگر ISAs کی طرح، اس پروسیسر کی تفصیلات آسانی سے مختلف ہدایات کے سیٹ لیولز کی وضاحت کرتی ہے۔ لہٰذا اس میں 32 اور 64 بٹ ویریئنٹس کے ساتھ ساتھ فلوٹنگ پوائنٹ ہدایات کو سپورٹ دینے کے لیے ایکسٹینشن بھی شامل ہیں۔

- یہ مفت، سادہ، ماڈیولر، مستحکم، وغیرہ ہیں۔

نقصانات

دی RISC V پروسیسر کے نقصانات مندرجہ ذیل شامل ہیں.

- کمپائلرز اور پروگرامرز کے ذریعہ پیچیدہ ہدایات اکثر استعمال ہوتی ہیں۔

- RISC کا o/p کوڈ کی بنیاد پر تبدیل ہو سکتا ہے جب ایک لوپ کے اندر آنے والی ہدایات عمل درآمد کے لیے پہلے کی ہدایات پر منحصر ہوتی ہیں۔

- ان پروسیسرز کو مختلف قسم کی ہدایات کو تیزی سے محفوظ کرنے کی ضرورت ہوتی ہے، جس کے لیے بروقت ہدایات کا جواب دینے کے لیے ایک بڑی کیش میموری سیٹ کی ضرورت ہوتی ہے۔

- RISC کی مکمل خصوصیات، صلاحیتیں اور فوائد بنیادی طور پر فن تعمیر پر منحصر ہیں۔

درخواستیں

دی RISC V کی درخواستیں پروسیسر مندرجہ ذیل شامل ہیں.

- RISC-V ایمبیڈڈ سسٹمز، مصنوعی ذہانت اور مشین لرننگ میں استعمال ہوتا ہے۔

- یہ پروسیسرز اعلی کارکردگی پر مبنی ایمبیڈڈ سسٹم ایپلی کیشنز میں استعمال ہوتے ہیں۔

- یہ پروسیسر کچھ خاص شعبوں جیسے ایج کمپیوٹنگ، AI اور اسٹوریج ایپلی کیشنز میں استعمال کرنے کے لیے موزوں ہے۔

- RISC-V اہم ہے کیونکہ یہ چھوٹے ڈیوائس مینوفیکچررز کو بغیر ادائیگی کے ہارڈ ویئر ڈیزائن کرنے کی اجازت دیتا ہے۔

- یہ پروسیسر صرف محققین اور ڈویلپرز کو آزادانہ طور پر دستیاب ISA یا انسٹرکشن سیٹ آرکیٹیکچر کے ساتھ ڈیزائن کے ساتھ ساتھ تحقیق کرنے کی اجازت دیتا ہے۔

- RISC V کی ایپلی کیشنز چھوٹے ایمبیڈڈ مائکروکنٹرولرز سے لے کر ڈیسک ٹاپ پی سی اور سپر کمپیوٹرز بشمول ویکٹر پروسیسرز تک ہیں۔

اس طرح، یہ ہے RISC V پروسیسر کا ایک جائزہ - فن تعمیر، ایپلی کیشنز کے ساتھ کام کرنا۔ یہاں آپ کے لیے ایک سوال ہے، CISC پروسیسر کیا ہے؟