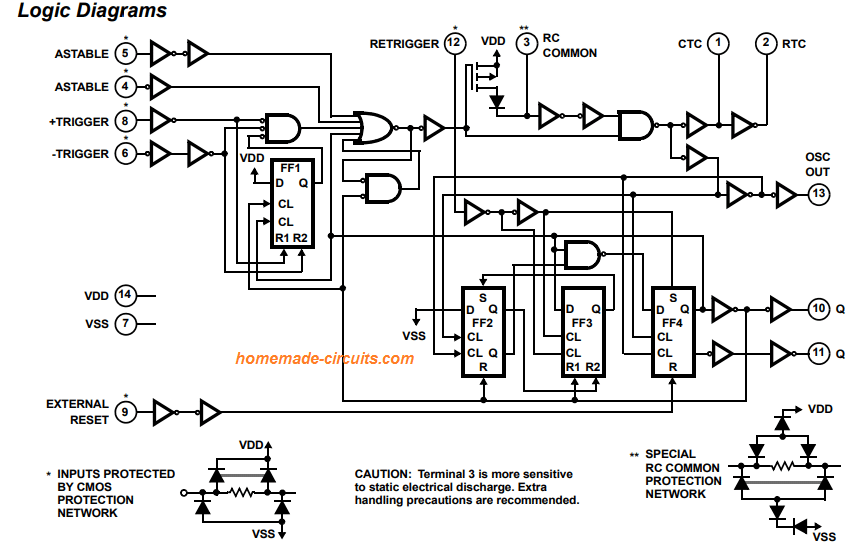

MOS ٹرانزسٹر بڑے پیمانے پر مربوط سرکٹ ڈیزائن میں سب سے بنیادی عنصر ہے۔ ان ٹرانزسٹروں کو عام طور پر دو اقسام PMOS اور NMOS میں تقسیم کیا جاتا ہے۔ NMOS اور PMOS ٹرانجسٹروں کے امتزاج کو a کہا جاتا ہے۔ CMOS ٹرانجسٹر . مختلف منطق کے دروازے اور دیگر ڈیجیٹل لاجک آلات جو لاگو ہوتے ہیں ان میں PMOS منطق کا ہونا ضروری ہے۔ یہ ٹیکنالوجی سستی ہے اور مداخلت کے خلاف اچھی مزاحمت رکھتی ہے۔ یہ مضمون MOS ٹرانزسٹروں کی ایک قسم جیسے PMOS ٹرانجسٹر پر بحث کرتا ہے۔

PMOS ٹرانجسٹر کیا ہے؟

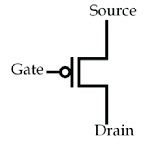

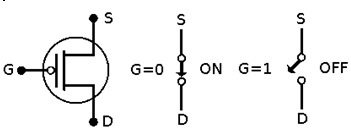

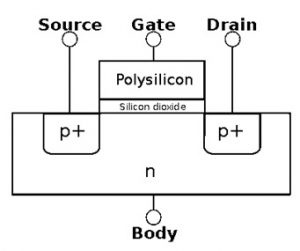

پی ایم او ایس ٹرانزسٹر یا پی چینل میٹل آکسائیڈ سیمی کنڈکٹر ایک قسم کا ٹرانزسٹر ہے جہاں پی قسم کے ڈوپینٹس کو چینل یا گیٹ کے علاقے میں استعمال کیا جاتا ہے۔ یہ ٹرانزسٹر بالکل NMOS ٹرانزسٹر کے الٹ ہے۔ ان ٹرانزسٹروں کے تین اہم ٹرمینلز ہیں۔ منبع، گیٹ اور ڈرین جہاں ٹرانجسٹر کا ماخذ پی قسم کے سبسٹریٹ کے ساتھ ڈیزائن کیا گیا ہے، اور ڈرین ٹرمینل کو این ٹائپ سبسٹریٹ کے ساتھ ڈیزائن کیا گیا ہے۔ اس ٹرانجسٹر میں، چارج کیریئر جیسے سوراخ کرنٹ کی ترسیل کے ذمہ دار ہوتے ہیں۔ PMOS ٹرانزسٹر کی علامتیں نیچے دکھائی گئی ہیں۔

PMOS ٹرانجسٹر کیسے کام کرتا ہے؟

پی ٹائپ ٹرانزسٹر کام کرنے والا این ٹائپ ٹرانجسٹر کے بالکل مخالف ہے۔ یہ ٹرانزسٹر ایک کھلا سرکٹ بنائے گا جب بھی اسے غیر معمولی وولٹیج ملے گا جس کا مطلب ہے کہ گیٹ (G) ٹرمینل سے سورس (S) تک بجلی کا کوئی بہاؤ نہیں ہے۔ اسی طرح، یہ ٹرانزسٹر ایک بند سرکٹ بناتا ہے جب اسے 0 وولٹ کے قریب وولٹیج ملتا ہے جس کا مطلب ہے کہ کرنٹ گیٹ (G) ٹرمینل سے ڈرین (D) کی طرف بہتا ہے۔

اس بلبلے کو الٹا بلبلا بھی کہا جاتا ہے۔ لہذا اس دائرے کا بنیادی کام ان پٹ وولٹیج کی قدر کو الٹنا ہے۔ اگر گیٹ ٹرمینل 1 وولٹیج فراہم کرتا ہے، تو یہ انورٹر اسے صفر میں بدل دے گا اور اس کے مطابق سرکٹ کو کام کرے گا۔ تو PMOS ٹرانزسٹر اور NMOS ٹرانزسٹر کا کام بالکل مخالف ہے۔ ایک بار جب ہم انہیں ایک واحد MOS سرکٹ میں ضم کر دیتے ہیں، تو یہ CMOS (کمپلیٹری میٹل آکسائیڈ سیمی کنڈکٹر) سرکٹ بن جائے گا۔

پی ایم او ایس ٹرانجسٹر کا کراس سیکشن

PMOS ٹرانجسٹر کا کراس سیکشن نیچے دکھایا گیا ہے۔ ایک پی ایم او ایس ٹرانزسٹر این ٹائپ باڈی کے ساتھ بنایا گیا ہے جس میں دو پی قسم کے سیمی کنڈکٹر ریجنز شامل ہیں جو گیٹ سے ملحق ہیں۔ اس ٹرانجسٹر میں ایک کنٹرولنگ گیٹ ہے جیسا کہ خاکہ میں دکھایا گیا ہے جو دو ٹرمینلز جیسے سورس اور ڈرین کے درمیان الیکٹران کے بہاؤ کو کنٹرول کرتا ہے۔ پی ایم او ایس ٹرانزسٹر میں جسم کو +ve وولٹیج پر رکھا جاتا ہے۔ ایک بار جب گیٹ ٹرمینل مثبت ہو جاتا ہے، تو پھر سورس اور ڈرین ٹرمینلز ریورس بایزڈ ہوتے ہیں۔ ایک بار ایسا ہونے کے بعد، کرنٹ کا کوئی بہاؤ نہیں ہے، اس لیے ٹرانزسٹر بند ہو جائے گا۔

ایک بار گیٹ ٹرمینل پر وولٹیج کی سپلائی کم ہونے کے بعد، مثبت چارج کیریئرز Si-SiO2 انٹرفیس کے نیچے کی طرف متوجہ ہوں گے۔ جب بھی وولٹیج کافی حد تک کم ہو جائے گا تو چینل الٹا ہو جائے گا اور کرنٹ کے بہاؤ کی اجازت دے کر سورس ٹرمینل سے ڈرین تک ایک کنڈکٹنگ پاتھ وے بنائے گا۔

جب بھی یہ ٹرانزسٹر ڈیجیٹل منطق سے نمٹتے ہیں تو عام طور پر دو مختلف قدریں ہوتی ہیں جیسے 1 اور 0 (آن اور آف)۔ ٹرانزسٹر کا مثبت وولٹیج VDD کے نام سے جانا جاتا ہے جو ڈیجیٹل سرکٹس کے اندر منطق کی اعلی (1) قدر کی نمائندگی کرتا ہے۔ VDD وولٹیج کی سطح میں ٹی ٹی ایل منطق عام طور پر 5V کے ارد گرد تھے. فی الوقت ٹرانزسٹر دراصل اتنے زیادہ وولٹیج کا مقابلہ نہیں کر سکتے کیونکہ وہ عام طور پر 1.5V - 3.3V کے درمیان ہوتے ہیں۔ کم وولٹیج کو اکثر GND یا VSS کہا جاتا ہے۔ لہذا، VSS منطق '0' کی نشاندہی کرتا ہے اور اسے عام طور پر 0V پر بھی سیٹ کیا جاتا ہے۔

پی ایم او ایس ٹرانزسٹر سرکٹ

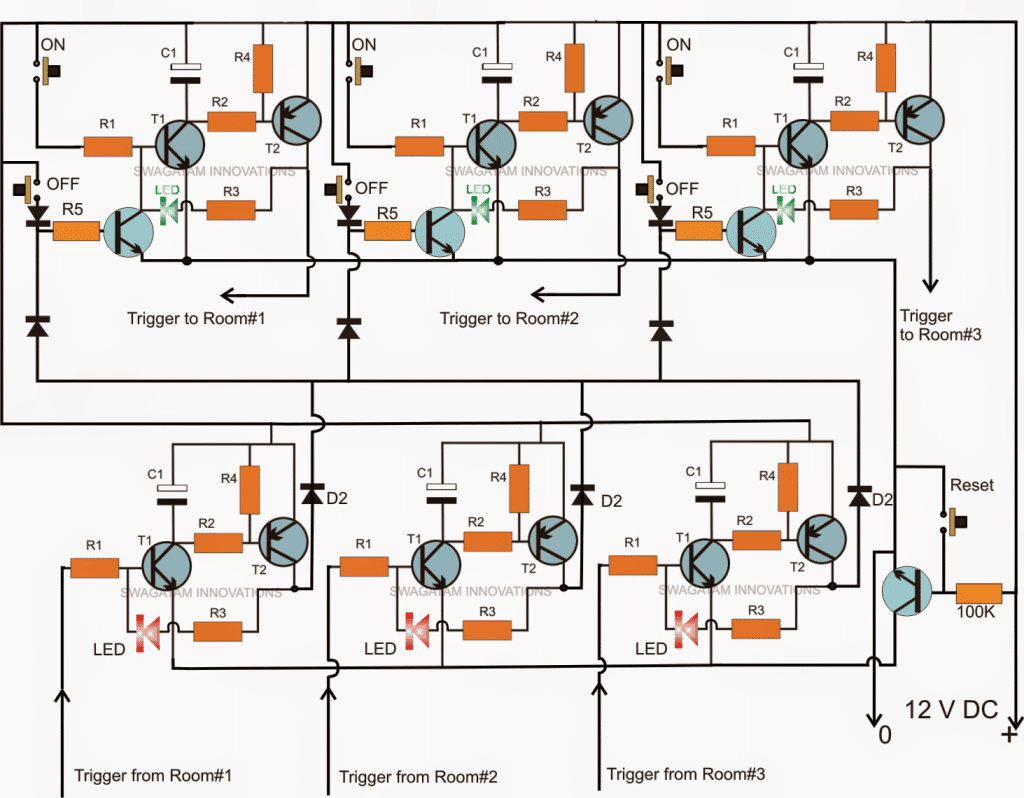

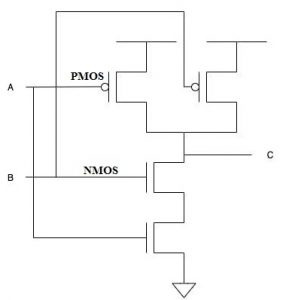

PMOS ٹرانجسٹر اور NMOS ٹرانجسٹر کا استعمال کرتے ہوئے NAND گیٹ کا ڈیزائن ذیل میں دکھایا گیا ہے۔ عام طور پر، ڈیجیٹل الیکٹرانکس میں NAND گیٹ ایک لاجک گیٹ ہوتا ہے جسے NOT-AND گیٹ بھی کہا جاتا ہے۔ اس گیٹ کا آؤٹ پٹ کم ہے (0) صرف اس صورت میں جب دو ان پٹ زیادہ ہوں (1) اور اس کی آؤٹ پٹ AND گیٹ کی تکمیل ہو۔ اگر دو ان پٹ میں سے کوئی بھی کم (0) ہے، تو یہ اعلی پیداوار کے نتائج دیتا ہے۔

نیچے دیے گئے لاجک سرکٹ میں، اگر ان پٹ A 0 ہے اور B 0 ہے، تو pMOS کا A ان پٹ '1' اور nMOS کا A ان پٹ '0' پیدا کرے گا۔ لہذا، یہ لاجک گیٹ ایک منطقی '1' پیدا کرتا ہے کیونکہ یہ ایک بند سرکٹ کے ذریعے منبع سے جڑا ہوتا ہے اور ایک کھلے سرکٹ کے ذریعے GND سے الگ ہوتا ہے۔

جب A '0' اور B' '1' ہے، تو pMOS کا ایک ان پٹ '1' پیدا کرے گا اور NMOS کا ایک ان پٹ '0' پیدا کرے گا۔ اس طرح، یہ گیٹ ایک منطقی پیدا کرے گا کیونکہ یہ ایک بند سرکٹ کے ذریعے منبع سے جڑا ہوا ہے اور ایک کھلے سرکٹ کے ذریعے GND سے الگ ہے۔ جب A '1' ہے اور B '0' ہے، تو pMOS کا 'B' ان پٹ ہائی آؤٹ پٹ (1) اور NMOS کا 'B' ان پٹ کم (0) آؤٹ پٹ پیدا کرے گا۔ لہذا، یہ لاجک گیٹ ایک منطقی 1 پیدا کرے گا کیونکہ یہ ایک بند سرکٹ کے ذریعے ماخذ سے جڑا ہوا ہے اور ایک کھلے سرکٹ کے ذریعے GND سے الگ ہے۔

جب A '1' ہے اور B '1' ہے، تو 'pMOS' کا ایک ان پٹ صفر پیدا کرے گا، اور nMOS کا ایک ان پٹ '1' پیدا کرے گا۔ اس کے نتیجے میں، ہمیں pMOS اور nMOS کے B ان پٹ کی بھی تصدیق کرنی چاہیے۔ pMOS کا B ان پٹ ایک '0' پیدا کرے گا اور nMOS کا B ان پٹ '1' پیدا کرے گا۔ لہذا، یہ لاجک گیٹ ایک منطقی '0' پیدا کرے گا کیونکہ یہ ایک کھلے سرکٹ کے ذریعہ منبع سے الگ ہوتا ہے اور بند سرکٹ کے ذریعے GND سے جڑا ہوتا ہے۔

سچائی کی میز

مندرجہ بالا لاجک سرکٹ کا سچ ٹیبل ذیل میں دیا گیا ہے۔

|

اے |

بی |

سی |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

PMOS ٹرانزسٹر کا تھریشولڈ وولٹیج عام طور پر 'Vgs' ہوتا ہے جو چینل بنانے کے لیے ضروری ہوتا ہے جسے چینل الٹا جانا جاتا ہے۔ پی ایم او ایس ٹرانزسٹر میں، سبسٹریٹ اور سورس ٹرمینلز آسانی سے 'Vdd' سے جڑے ہوتے ہیں۔ اگر ہم Vdd سے گیٹ ٹرمینل پر سورس ٹرمینل کے حوالے سے وولٹیج کو کم کرنا شروع کر دیتے ہیں جہاں بھی آپ کو چینل کا الٹا نظر آتا ہے، اس پوزیشن پر اگر آپ Vgs اور سورس کے اعلیٰ صلاحیت پر ہونے کا تجزیہ کرتے ہیں، تو آپ کو منفی قدر ملے گی۔ لہذا، PMOS ٹرانجسٹر کی Vth قدر منفی ہے۔

پی ایم او ایس بنانے کا عمل

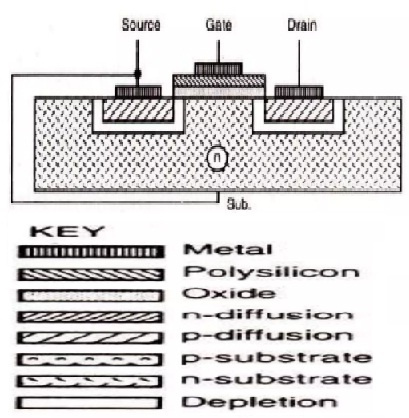

پی ایم او ایس ٹرانجسٹر فیبریکیشن میں شامل اقدامات ذیل میں زیر بحث آئے ہیں۔

مرحلہ نمبر 1:

ایک پتلی سیلیکون ویفر پرت کو صرف فاسفورس مواد کی ڈوپنگ کے ذریعے N قسم کے مواد میں تبدیل کیا جاتا ہے۔

مرحلہ 2:

ایک موٹی سیلیکون ڈائی آکسائیڈ (Sio2) تہہ ایک مکمل p قسم کے سبسٹریٹ پر اگائی جاتی ہے۔

مرحلہ 3:

اب سطح موٹی سلکان ڈائی آکسائیڈ پرت کے اوپر فوٹو ریزسٹ کے ساتھ لیپت ہے۔

مرحلہ 4:

اس کے بعد، اس تہہ کو صرف ایک ماسک کے ذریعے UV روشنی کے سامنے لایا جاتا ہے جو ان خطوں کی وضاحت کرتا ہے جن میں ٹرانسسٹر چینلز کے ساتھ مل کر پھیلنا ہوتا ہے۔

مرحلہ 5:

ان خطوں کو بنیادی طور پر سلکان ڈائی آکسائیڈ کے ساتھ جوڑ دیا جاتا ہے تاکہ ویفر کی سطح ماسک کے ذریعہ بیان کردہ کھڑکی کے اندر سامنے آجائے۔

مرحلہ 6:

بقیہ فوٹو ریزسٹ الگ ہے اور پتلی Sio2 تہہ عام طور پر چپ کی پوری سطح پر 0.1 مائیکرو میٹر بڑھائی جاتی ہے۔ اس کے بعد، گیٹ کی ساخت بنانے کے لیے پولی سیلیکون کو اس پر رکھا جاتا ہے۔ ایک فوٹو ریزسٹ کو پولی سیلیکون کی پوری تہہ پر رکھا جاتا ہے اور ماسک 2 کے ذریعے UV روشنی کو بے نقاب کرتا ہے۔

مرحلہ 7:

ڈفیوژن زیادہ سے زیادہ درجہ حرارت تک ویفر ہیٹنگ کے ذریعے حاصل کیا جاتا ہے اور بورون جیسی مطلوبہ پی قسم کی نجاست کے ساتھ گیس گزر جاتی ہے۔

مرحلہ 8:

1 مائیکرو میٹر موٹائی سلکان ڈائی آکسائیڈ اگائی جاتی ہے اور اس پر فوٹو ریزسٹ مواد جمع کیا جاتا ہے۔ بالائے بنفشی روشنی کو ماسک 3 کے ساتھ گیٹ، سورس اور ڈرین کے ترجیحی جگہوں پر لگائیں جو رابطہ کٹنے کے لیے کھدائی گئی ہیں۔

مرحلہ 9:

اب ایک دھات یا ایلومینیم اس کی 1 مائکرو میٹر موٹائی کی سطح پر جمع ہے۔ ایک بار پھر ایک فوٹو ریزسٹ مواد کو پوری دھات پر اگایا جاتا ہے اور ماسک 4 کے ذریعے UV لائٹ کو بے نقاب کیا جاتا ہے جسے مطلوبہ انٹر کنکشن ڈیزائن بنانے کے لیے اینچ کیا جاتا ہے۔ حتمی PMOS ڈھانچہ ذیل میں دکھایا گیا ہے۔

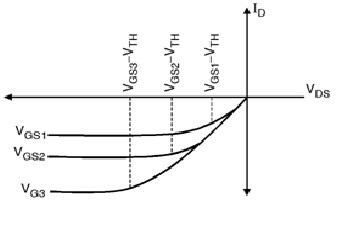

پی ایم او ایس ٹرانزسٹر کی خصوصیات

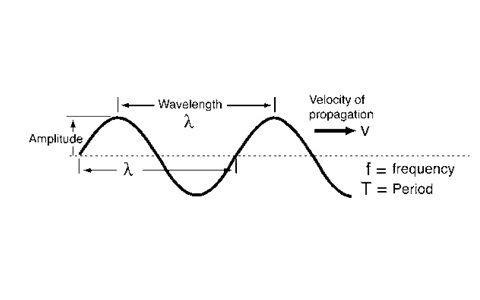

PMOS ٹرانزسٹر I-V کی خصوصیات ذیل میں دکھائی گئی ہیں۔ ڈرین ٹو سورس کرنٹ (I DS) کے ساتھ ساتھ اس کے ٹرمینل وولٹیج جیسے لکیری اور سنترپتی علاقوں کے درمیان تعلق حاصل کرنے کے لیے ان خصوصیات کو دو خطوں میں تقسیم کیا گیا ہے۔

لائنر ریجن میں، IDS لکیری طور پر بڑھے گا جب VDS (ڈرین ٹو سورس وولٹیج) میں اضافہ ہوتا ہے جبکہ سیچوریشن ریجن میں، I DS مستحکم ہوتا ہے اور یہ VDS سے آزاد ہوتا ہے۔ ISD (کرنٹ نکالنے کا ذریعہ) اور اس کے ٹرمینل وولٹیجز کے درمیان بنیادی تعلق NMOS ٹرانزسٹر کے اسی طرح کے طریقہ کار سے اخذ کیا گیا ہے۔ اس صورت میں، صرف تبدیلی یہ ہوگی کہ الٹی پرت کے اندر موجود چارج کیریئرز صرف سوراخ ہیں۔ جب سوراخ ماخذ سے نالی کی طرف جاتے ہیں تو کرنٹ کا بہاؤ بھی ایک جیسا ہوتا ہے۔

اس طرح، منفی نشان موجودہ مساوات کے اندر ظاہر ہوتا ہے. اس کے علاوہ، آلے کے ٹرمینلز پر لگائے گئے تمام تعصبات منفی ہیں۔ لہذا، PMOS ٹرانزسٹر کی ID - VDS کی خصوصیات ذیل میں دکھائی گئی ہیں۔

لکیری خطے میں PMOS ٹرانجسٹر کے لیے ڈرین کرنٹ کی مساوات اس طرح دی گئی ہے:

ID = – ایم پی کاکس

اسی طرح، سنترپتی خطے میں PMOS ٹرانجسٹر کے لیے ڈرین کرنٹ مساوات کو اس طرح دیا گیا ہے:

ID = – mp Cox (VSG – | V TH |p )^2

جہاں 'mp' سوراخ کی نقل و حرکت ہے اور '|VTH| p' PMOS ٹرانجسٹر کی تھریشولڈ وولٹیج ہے۔

مندرجہ بالا مساوات میں، منفی نشان اشارہ کرے گا کہ ID( نالی کرنٹ ) ڈرین (D) سے ماخذ (S) کی طرف بہتا ہے جبکہ سوراخ مخالف سمت میں بہتے ہیں۔ جب سوراخ کی نقل و حرکت الیکٹران کی نقل و حرکت کے مقابلے میں کم ہوتی ہے تو پھر PMOS ٹرانجسٹر کم کرنٹ ڈرائیو کی صلاحیت سے متاثر ہوتے ہیں۔

اس طرح، یہ سب PMOS ٹرانزسٹر یا p-type MOs ٹرانزسٹر - فیبریکیشن، سرکٹ، اور اس کے کام کے ایک جائزہ کے بارے میں ہے۔ پی ایم او ایس ٹرانجسٹرز ڈیزائن کیے گئے ہیں۔ پی سورس، این سبسٹریٹ اور ڈرین کے ساتھ۔ PMOS کے چارج کیریئر سوراخ ہیں۔ یہ ٹرانزسٹر گیٹ ٹرمینل پر کم وولٹیج لگانے کے بعد چلاتا ہے۔ NMOS آلات کے مقابلے PMOS پر مبنی آلات مداخلت کا کم شکار ہوتے ہیں۔ ان ٹرانزسٹروں کو وولٹیج پر قابو پانے والے ریزسٹرس، ایکٹو لوڈز، کرنٹ آئینے، ٹرانس امپیڈینس ایمپلیفائر کے طور پر استعمال کیا جا سکتا ہے، اور سوئچز اور وولٹیج ایمپلیفائر میں بھی استعمال کیا جا سکتا ہے۔ یہاں آپ کے لیے ایک سوال ہے، NMOS ٹرانزسٹر کیا ہے؟