ای سی ایل (ایمیٹر کپلڈ لاجک) پہلی بار IBM میں اگست 1956 میں Hannon S. Yourke نے ایجاد کیا تھا۔ اس منطق کو کرنٹ موڈ لاجک کے نام سے بھی جانا جاتا ہے، جو IBM 7090 اور 7094 کے کمپیوٹرز میں استعمال ہوتا ہے۔ ECL فیملی کے مقابلے میں بہت تیز ہے۔ ڈیجیٹل منطق خاندانوں عام طور پر، یہ منطق فیملی 1 ns سے کم کی تبلیغ میں تاخیر فراہم کرتی ہے۔ یہ دو قطبی جنکشن ٹرانزسٹرز پر مبنی ایک منطقی خاندان ہے۔ یہ ایک تیز ترین منطق فیملی سرکٹ ہے جو روایتی منطقی نظام کو ڈیزائن کرنے کے لیے قابل رسائی ہے۔ یہ مضمون ایک کے جائزہ پر بحث کرتا ہے۔ ایمیٹر کپلڈ منطق – سرکٹ ، ایپلی کیشنز کے ساتھ کام کرنا۔

Emitter Coupled Logic کیا ہے؟

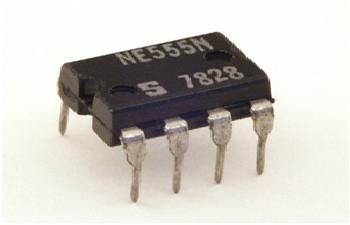

ایمیٹر کپلڈ منطق بہترین ہے۔ بی جے ٹی روایتی منطق کے نظام کے ڈیزائن میں استعمال ہونے والا منطقی خاندان۔ بعض اوقات، اسے کرنٹ موڈ لاجک بھی کہا جاتا ہے جو کہ ایک بہت تیز رفتار ڈیجیٹل ٹیکنالوجی ہے۔ عام طور پر، ای سی ایل کو تیز ترین لاجک آئی سی کے طور پر سمجھا جاتا ہے جہاں یہ بہت کم وولٹیج سوئنگ کا استعمال کرتے ہوئے اور ٹرانجسٹروں کو سنترپتی علاقے میں داخل ہونے سے بھی گریز کرکے اپنا تیز رفتار آپریشن حاصل کرتا ہے۔

ECL کا نفاذ ایک مثبت سپلائی وولٹیج کا استعمال کرتا ہے جسے PECL یا مثبت حوالہ ECL کہا جاتا ہے۔ ابتدائی ای سی ایل گیٹس میں، شور کی قوت مدافعت کی وجہ سے منفی وولٹیج کی فراہمی کا استعمال کیا جاتا ہے۔ اس کے بعد، مثبت حوالہ شدہ ECL TTL لاجک فیملیز کے مقابلے میں زیادہ مطابقت پذیر منطق کی سطح کی وجہ سے بہت مشہور ہوا۔

Emitter-compled logic جامد طاقت کی ایک بہت بڑی مقدار کو ضائع کر دیتی ہے، تاہم، اس کی کرنٹ کی مجموعی کھپت اس کے مقابلے میں کم ہے۔ CMOS اعلی تعدد پر. لہذا، ای سی ایل بنیادی طور پر کلاک ڈسٹری بیوشن سرکٹس اور ہائی فریکونسی پر مبنی ایپلی کیشنز میں فائدہ مند ہے۔

ایمیٹر کپلڈ منطق کی خصوصیات

ای سی ایل کی خصوصیات ان کو بہت سی اعلیٰ کارکردگی پر مبنی ایپلی کیشنز میں استعمال کرائیں گی۔

- ای سی ایل دو آؤٹ پٹ فراہم کرتا ہے جو ہمیشہ ایک دوسرے کے تکمیلی ہوتے ہیں کیونکہ، سرکٹ کا آپریشن ایک ڈیفرینشل ایمپلیفائر پر مبنی ہوتا ہے۔

- یہ منطق کا خاندان بنیادی طور پر یک سنگی ساخت کے طریقوں کے لیے موزوں ہے کیونکہ منطق کی سطحیں ریزسٹر ریشوز کا کام ہیں۔

- ای سی ایل فیملی کے آلات کسی بھی بیرونی انورٹر کا استعمال کیے بغیر مجوزہ فنکشن کا صحیح اور تکمیلی آؤٹ پٹ تیار کرتے ہیں۔ نتیجتاً، یہ پیکج کی گنتی، اور بجلی کی ضروریات کو کم کرتا ہے اور وقت کی تاخیر سے پیدا ہونے والے مسائل کو بھی کم کرتا ہے۔

- ڈیفرینشل ایمپلیفائر ڈیزائن میں ای سی ایل ڈیوائسز وسیع کارکردگی کی لچک پیش کرتی ہیں، لہذا ای سی ایل سرکٹس ڈیجیٹل اور لکیری سرکٹس دونوں کے طور پر استعمال ہونے کی اجازت دیتے ہیں۔

- ای سی ایل گیٹ کے ڈیزائن میں عام طور پر زیادہ اور کم ان پٹ رکاوٹ ہوتی ہے، جو بڑے پنکھے کے آؤٹ ہونے کے ساتھ ساتھ ڈرائیو کی صلاحیت کو حاصل کرنے کے لیے انتہائی موزوں ہے۔

- ای سی ایل ڈیوائسز پاور سپلائی کے ڈیزائن کو آسان بنانے کے لیے پاور سپلائی پر مستقل کرنٹ پیدا کرتی ہیں۔

- ای سی ایل کے آلات بشمول اوپن ایمیٹر آؤٹ پٹس انہیں آسانی سے ٹرانسمیشن لائن ڈرائیو کی گنجائش کو شامل کرنے کی اجازت دیتے ہیں۔

ایمیٹر کپلڈ لاجک سرکٹ

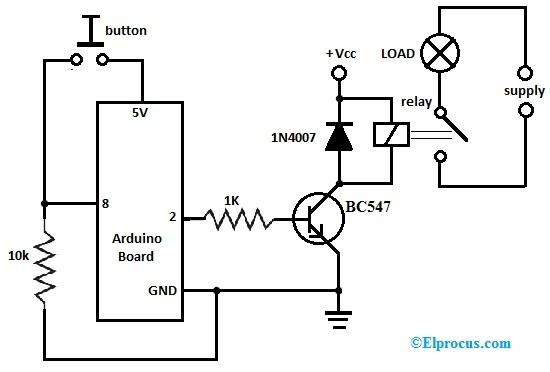

انورٹر کے لیے ایمیٹر کپلڈ لاجک سرکٹ نیچے دکھایا گیا ہے جسے ریزسٹرس اور ٹرانزسٹرز کے ساتھ ڈیزائن کیا گیا ہے۔ اس سرکٹ میں، دو ٹرانجسٹروں کے ایمیٹر ٹرمینلز کو کرنٹ محدود کرنے والی مزاحمت RE سے آسانی سے جوڑا جاتا ہے جو ٹرانزسٹر کو سنترپتی میں داخل ہونے سے روکنے کے لیے استعمال ہوتا ہے۔ یہاں ٹرانزسٹر کا آؤٹ پٹ ایمیٹر ٹرمینل کے بجائے کلکٹر ٹرمینل سے لیا جاتا ہے۔ یہ سرکٹ دو آؤٹ پٹ Vout (انورٹنگ آؤٹ پٹ) اور Vout2 (نان انورٹنگ آؤٹ پٹ) اور ان پٹ ٹرمینل فراہم کرتا ہے جیسے Vin جہاں زیادہ یا کم ان پٹ دیا جاتا ہے۔ +Vcc = 5V۔

ایمیٹر کپلڈ منطق کیسے کام کرتی ہے؟

ایمیٹر کپلڈ لاجک کا آپریشن یہ ہے کہ جب بھی ای سی ایل سرکٹ کو ہائی ان پٹ دیا جاتا ہے، تو یہ 'Q1' ٹرانزسٹر کو آن اور Q2 ٹرانزسٹر کو بند کر دیتا ہے لیکن Q1 ٹرانزسٹر سیر نہیں ہوتا ہے۔ تو یہ VOUT2 آؤٹ پٹ کو ہائی پر لے جائے گا اور R1 کے اندر گرنے کی وجہ سے VOUT1 آؤٹ پٹ کی قدر کم ہوگی۔

اسی طرح، جب ECL کو دی گئی VIN ویلیو کم ہے، تو یہ Q1 ٹرانزسٹر کو آف اور Q2 ٹرانزسٹر کو آن کر دے گا۔ لہذا، Q2 ٹرانجسٹر سنترپتی میں نہیں جائے گا. لہذا یہ VOUT1 آؤٹ پٹ کو ہائی ویلیو بنائے گا اور VOUT2 آؤٹ پٹ ویلیو R2 مزاحمت کے اندر گرنے کی وجہ سے کم ہوگی۔

آئیے دیکھتے ہیں کہ جب وولٹیج لگائی جاتی ہے تو ٹرانزسٹر Q1 اور Q2 کیسے آن اور آف ہوتے ہیں۔

اس سرکٹ میں Q1 اور Q2 جیسے دو ٹرانزسٹر ایک عام ایمیٹر ریزسٹر کے ذریعے ایک ڈیفرینشل ایمپلیفائر کے طور پر جڑے ہوئے ہیں۔

اس مثال کے سرکٹ کے لیے وولٹیج کی فراہمی VCC = 5.0، VBB = 4.0 اور VEE = 0 V ہیں۔ ان پٹ ہائی اور لو لیول کی قدروں کو صرف 4.4 V اور 3.6V میں بیان کیا گیا ہے۔ درحقیقت، یہ سرکٹ کم آؤٹ پٹ اور ہائی لیول پیدا کرتا ہے جو کہ 0.6 وولٹ زیادہ ہیں۔ تاہم، یہ حقیقی ECL سرکٹس میں درست کیا جاتا ہے۔

ایک بار جب Vin ہائی ہو جاتا ہے، تو Q1 ٹرانزسٹر آن ہو جاتا ہے، تاہم سیر نہیں ہوتا اور Q2 ٹرانزسٹر آف ہو جاتا ہے۔ لہذا، VOUT2 جیسے آؤٹ پٹ وولٹیج کو R2 ریزسٹر کے ذریعے 5 V تک کھینچا جاتا ہے اور یہ دکھایا جا سکتا ہے کہ R1 ریزسٹر کے پار وولٹیج کا ڈراپ تقریباً 0.8 V ہے تاکہ VOUT1 = 4.2 V (LOW)۔ اس کے علاوہ VE = VOUT1 - VQ1 => 4.2V - 0.4V = 3.8V کیونکہ ٹرانزسٹر Q1 مکمل طور پر آن ہے۔

ون کم ہونے کے بعد، Q2 ٹرانزسٹر آن ہو جائے گا، لیکن سیر نہیں ہوگا اور Q1 ٹرانزسٹر آف ہو جائے گا۔ لہذا، VOUT1 کو R1 ریزسٹر کا استعمال کرتے ہوئے 5.0 V پر کھینچا جاتا ہے اور یہ دکھایا جا سکتا ہے کہ VOUT2 4.2 V ہے۔ اس کے علاوہ VE => VOUT2 – VQ2 => 4.2V – 0.8V => 3.4V جیسے ہی ٹرانجسٹر Q2 آن ہوتا ہے۔

ای سی ایل میں، دو ٹرانجسٹر کبھی بھی ٹی کے طور پر سنترپتی میں نہیں ہوتے ہیں۔ ان پٹ/آؤٹ پٹ وولٹیج کے جھولے کافی چھوٹے ہیں جیسے 0.8v اور ان پٹ کی رکاوٹ زیادہ ہے اور آؤٹ پٹ مزاحمت کم ہے۔ اس سے ECL کو تیزی سے کام کرنے میں مدد ملتی ہے جس میں کم پروپیگیشن تاخیر کا وقت ہوتا ہے۔

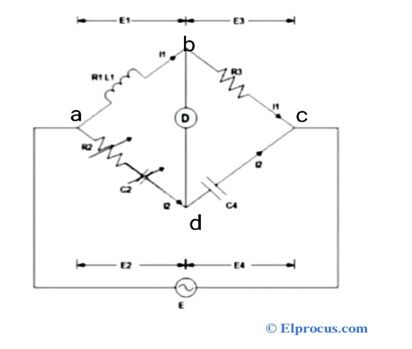

دو ان پٹ ایمیٹر کپلڈ لاجک OR/NOR گیٹ سرکٹ

دو ان پٹ ایمیٹر جوڑے ہوئے منطق OR/NOR گیٹ سرکٹ ذیل میں دکھایا گیا ہے۔ اس سرکٹ کو اوپر والے انورٹر سرکٹ میں ترمیم کرکے ڈیزائن کیا گیا ہے۔ ترمیم ان پٹ سائیڈ پر ایک اضافی ٹرانزسٹر شامل کرکے ہے۔

اس سرکٹ کا کام بہت آسان ہے۔ جب Q1 اور Q2 دونوں ٹرانزسٹروں پر لاگو ہونے والے ان پٹ کم ہوں گے تو آؤٹ پٹ 1 (Vout1) کو ہائی ویلیو بنا دے گا۔ لہذا، یہ Vout1 NOR گیٹ کے آؤٹ پٹ سے مطابقت رکھتا ہے۔

اس کے ساتھ ہی، اگر Q3 ٹرانزسٹر کو آن کیا جاتا ہے، تو یہ دوسری آؤٹ پٹ (Vout2) کو ہائی بنائے گا۔ لہذا، یہ Vou2 آؤٹ پٹ OR گیٹ آؤٹ پٹ سے مساوی ہے۔

اسی طرح، اگر دونوں Q1 اور Q2 ٹرانزسٹر ان پٹ زیادہ ہیں، تو یہ Q1 اور Q2 ٹرانزسٹر کو آن کر دے گا اور VOUT1 ٹرمینل پر کم آؤٹ پٹ فراہم کرے گا۔

اگر اس آپریشن کے دوران Q3 ٹرانزسٹر آف کر دیا جاتا ہے تو یہ VOUT2 ٹرمینل پر اعلیٰ پیداوار فراہم کرے گا۔ لہذا، OR/NOR گیٹ کے لیے سچائی کی میز ذیل میں دی گئی ہے۔

|

ان پٹ |

ان پٹ | یا |

NOR |

|

اے |

بی | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

ایمیٹر-کپلڈ منطق کی خصوصیات

ای سی ایل کی خصوصیات میں درج ذیل شامل ہیں۔

- TTL کے مقابلے میں، ECL کا پھیلاؤ کا وقت 0.5 سے 2 ns تک ہوتا ہے۔ لیکن، 30 میگاواٹ جیسے ٹی ٹی ایل کے مقابلے میں ایمیٹر کپلڈ لاجک پاور ڈسپیشن زیادہ ہے۔

- ECL کے I/O وولٹیجز میں 0.8 کی طرح ایک چھوٹا سا جھول ہوتا ہے۔

- ای سی ایل کی ان پٹ رکاوٹ زیادہ ہے اور آؤٹ پٹ مزاحمت کم ہے۔ نتیجتاً، ٹرانجسٹر اپنی حالتوں کو بہت تیزی سے تبدیل کرتا ہے۔

- ECLs فین آؤٹ کی گنجائش زیادہ ہے اور گیٹ میں تاخیر کم ہے۔

- ECL کی O/p منطق کم سے اعلی حالت میں بدل جاتی ہے لیکن ان ریاستوں کے لیے وولٹیج کی سطحیں TTL اور EC کے درمیان مختلف ہوں گی۔

- ای سی ایل کی شور کی قوت مدافعت 0.4V ہے۔

فائدے اور نقصانات

دی ایمیٹر کپلڈ منطق کے فوائد ذیل میں بحث کی جاتی ہے.

- ECL کا فین آؤٹ 25 ہے جو TTL کے مقابلے میں بہتر ہے اور یہ CMOS کے مقابلے میں کم ہے۔

- ای سی ایل کا اوسط پروپیگیشن تاخیر کا وقت 1 سے 4 این ایس ہے جو CMOS اور دونوں کے مقابلے میں بہتر ہے۔

- ٹی ٹی ایل اس طرح اسے تیز ترین منطق کا خاندان کہا جاتا ہے۔

- جب ایمیٹر میں BJTs جوڑے منطق کے دروازے فعال علاقے میں کام کرتے ہیں، پھر ان کی رفتار تمام منطقی خاندانوں کے مقابلے میں زیادہ ہوتی ہے۔

- ای سی ایل گیٹس تکمیلی پیداوار پیدا کرتے ہیں۔

- پاور سپلائی لیڈز میں موجودہ سوئچنگ اسپائکس نہیں ہیں۔

- وائرڈ-یا فنکشن فراہم کرنے کے لیے آؤٹ پٹ کو مشترکہ طور پر جوڑا جا سکتا ہے۔

- ای سی ایل کے پیرامیٹرز درجہ حرارت کے ذریعے زیادہ تبدیل نہیں ہوتے ہیں۔

- نمبر صرف ایک چپ سے قابل رسائی افعال کی تعداد زیادہ ہے۔

دی ایمیٹر کپلڈ منطق کے نقصانات ذیل میں بحث کی جاتی ہے.

- اس میں انتہائی کم شور مارجن ہے یعنی ±200 mV۔

- دیگر منطقی دروازوں کے مقابلے میں بجلی کی کھپت زیادہ ہے۔

- دوسرے منطقی خاندانوں کے ساتھ انٹرفیس کرنے کے لیے، لیول شفٹرز ضروری ہیں۔

- Fanout capacitive لوڈنگ کو محدود کرتا ہے۔

- کے مقابلے میں ٹی ٹی ایل ، ای سی ایل کے دروازے مہنگے ہیں۔

- CMOS اور TTL کے مقابلے میں، ECL شور سے استثنیٰ سب سے خراب ہے۔

ایپلی کیشنز

ایمیٹر کپلڈ منطق کے استعمال میں درج ذیل شامل ہیں۔

- ایمیٹر کپلڈ لاجک کو انتہائی تیز رفتار مواصلاتی آلات جیسے فائبر آپٹک ٹرانسیور انٹرفیس، ایتھرنیٹ اور اے ٹی ایم (ایسینکرونس ٹرانسفر موڈ) نیٹ ورکس میں ایک منطق اور انٹرفیس ٹیکنالوجی کے طور پر استعمال کیا جاتا ہے۔

- ای سی ایل بی جے ٹی پر مبنی ایک منطقی خاندان ہے جہاں نسبتاً چھوٹے وولٹیج کے جھولے کا استعمال کرتے ہوئے اور ٹرانزسٹروں کو سیچوریشن ریجن میں جانے سے گریز کرکے اس کا تیز رفتار آپریشن حاصل کیا جاسکتا ہے۔

- ECL IBM 360/91 کے اندر ASLT سرکٹس بنانے میں استعمال ہوتا ہے۔

- ای سی ایل انورٹر فنکشن حاصل کرنے کے لیے پرائمری اور سیکنڈری ٹرانزسٹرز کے درمیان سنگل اینڈڈ بائیس i/p اور مثبت فیڈ بیک کا استعمال کرکے اسٹیکڈ ٹرانزسٹروں کے استعمال سے گریز کرتا ہے۔

- ECL انتہائی تیز رفتار الیکٹرانکس میں استعمال ہوتا ہے۔

اس طرح، یہ ہے ایک ایمیٹر جوڑے منطق کا جائزہ یا ای سی ایل – سرکٹ، ورکنگ، فیچرز، خصوصیات، اور ایپلیکیشنز۔ ECL دیگر ڈیجیٹل لاجک فیملیز کے مقابلے BJT پر مبنی بہت تیز ترین لاجک فیملی ہے۔ یہ ایک چھوٹی وولٹیج سوئنگ کا استعمال کرتے ہوئے اور ٹرانجسٹروں کو سنترپتی خطے میں جانے سے گریز کرکے اپنی زیادہ سے زیادہ رفتار کو حاصل کرتا ہے۔ یہ لاجک فیملی ایک ناقابل یقین 1ns پروپیگیشن تاخیر فراہم کرتی ہے اور تازہ ترین ECL فیملیز میں اس تاخیر کو کم کیا گیا ہے۔ یہاں آپ کے لیے ایک سوال ہے کہ ای سی ایل کے لیے متبادل نام کیا ہے؟